People sometimes say that some digital signal has "TTL levels".

What are these levels and where can I find them?

I searched the Internet and found sources claiming slightly different numbers. Fortunately, there appears to be agreement on the most important levels.

Summary

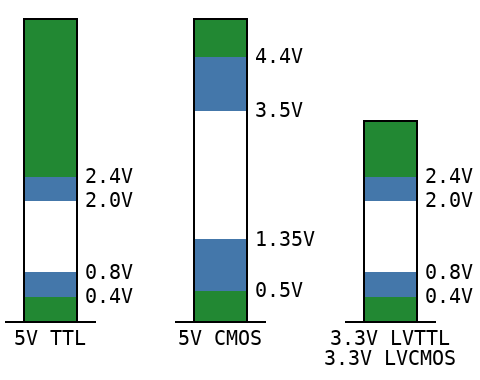

This is my best guess based on the sources I found:

| Logic standard | VIL | VIH | VOL | VOH |

|---|---|---|---|---|

| 5V TTL | 0.8 V | 2.0 V | 0.4 V | 2.4 V |

| 5V CMOS | 1.35 V | 3.5 V | 0.5 V | 4.4 V |

| 3.3V LVTTL | 0.8 V | 2.0 V | 0.4 V | 2.4 V |

| 3.3V LVCMOS | 0.8 V | 2.0 V | 0.4 V | 2.4 V |

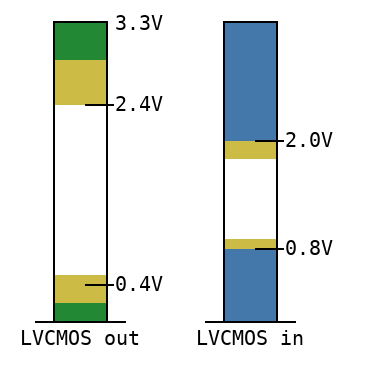

green = guaranteed output range; blue = safe input levels

What are these levels?

VIL = Highest voltage that receivers will reliably detect as LOW state.

VIH = Lowest voltage that receivers will reliably detect as HIGH state.

VOL = Highest allowed output voltage in LOW state.

VOH = Lowest allowed output voltage in HIGH state.

Please keep in mind that these threshold voltages are only one aspect of a digital interface. There are more things to consider before you connect two digital signals to each other. For example, connecting a 5V TTL driver to a 3.3 V LVCMOS receiver, will likely damage the receiver because its input voltage will be too high.

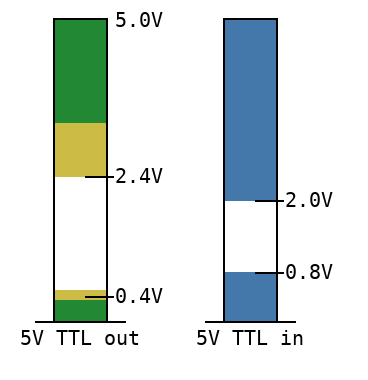

5V TTL

There is unanimous agreement about the TTL input levels in all sources I found. So at least that much is clear.

A few different numbers can be found for output levels. I picked the ones that are most commonly stated.

green = ideal output levels; blue = safe input levels; yellow = disputed levels

| Level | Value | References |

|---|---|---|

| VIL | 0.8 V | [1] [2] [3] [4] [5] [6] [7] [8] [9] [12] [13] |

| VIH | 2.0 V | [1] [2] [3] [4] [5] [6] [7] [8] [9] [12] [13] |

| VOL | 0.35 V | [6] |

| 0.4 V | [2] [4] [5] [7] [9] [12] | |

| 0.5 V | [8] | |

| VOH | 2.4 V | [2] [5] [9] [12] [4] |

| 2.7 V | [7] [8] | |

| 3.3 V | [6] |

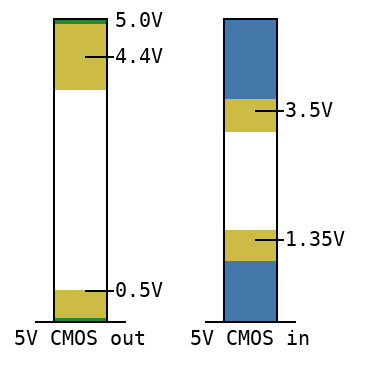

5V CMOS

Different sources state very different voltages for CMOS logic. Perhaps because the thresholds depend on the power supply voltage and on the kind of CMOS technology.

Which of these numbers are correct? I really can't say.

| Level | Value | References |

|---|---|---|

| VIL | 1.0 V | [3] |

| 1.3 V | [6] | |

| 1.35 V | [4] | |

| 1.5 V | [3] [5] [8] [10] | |

| VIH | 3.15 V | [4] |

| 3.5 V | [3] [5] [8] [10] | |

| 3.7 V | [6] | |

| VOL | 0.05 V | [8] [10] |

| 0.1 V | [3] [13] | |

| 0.2 V | [6] | |

| 0.33 V | [4] | |

| 0.5 V | [3] [5] | |

| VOH | 3.84 V | [4] |

| 4.4 V | [5] [13] | |

| 4.5 V | [3] | |

| 4.7 V | [6] | |

| 4.9 V | [3] | |

| 4.95 V | [8] [10] |

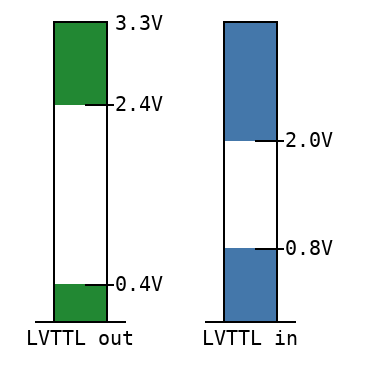

3.3V LVTTL

Everybody agrees on all LVTTL thresholds. Great!

| Level | Value | References |

|---|---|---|

| VIL | 0.8 V | [4] [5] [14] [15] |

| VIH | 2.0 V | [4] [5] [14] [15] |

| VOL | 0.4 V | [4] [5] [14] [15] |

| VOH | 2.4 V | [4] [5] [14] [15] |

3.3V LVCMOS

Opinions on LVCMOS levels vary. Just pick one, I guess.

| Level | Value | References |

|---|---|---|

| VIL | 0.8 V | [6] [7] [11] [14] [15] |

| 0.9 V | [4] | |

| VIH | 1.8 V | [4] |

| 2.0 V | [6] [7] [11] [14] [15] | |

| VOL | 0.2 V | [14] |

| 0.36 V | [4] | |

| 0.4 V | [6] [11] [15] | |

| 0.5 V | [7] | |

| VOH | 2.4 V | [6] [7] [11] |

| 2.7 V | [4] | |

| 2.8 V | [14] | |

| 2.9 V | [15] |

References

1. Wikipedia, Logic level

2. Wikipedia: Transistor-transistor logic

3. Wikipedia, 7400-series intergated circuits

4. D. Harris, S. Harris, Digital Design and Computer Architecture.

5. Texas Instruments, Logic Guide 2017

6. Interfacebus, Logic Threshold Voltage Levels

7. Sparkfun, Logic Levels

8. AllAboutCircuits, Digital Circuits: Logic Signal Voltage Levels

9. StackExchange, Output voltage level of TTL gate

10. RCA, CD4000B datasheet

11. Texas Instruments, SN74LVC1G04 datasheet

12. Texas Instruments, SN7400 datasheet

13. Texas Instruments, SN74HCT00 datasheet

14.

JEDEC, JESD8C: Interface Standard for 3V, 3.3V Supply Digital ICs.

(JEDEC tries to keep this document secret. Search the internet for "jesd8c" to find the PDF.)

15. Xilinx, Spartan 3 datasheet (ds099)